## Hardware Design I Chap. 2 Basis of logical circuit, logical expression, and logical function

Computing Architecture Lab.

Hajime Shimada

E-mail: shimada@is.naist.jp

1

### Outline

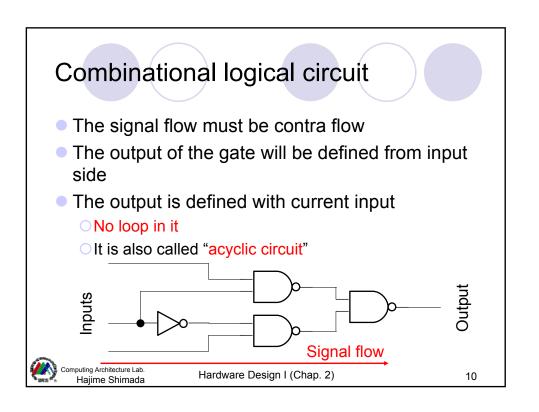

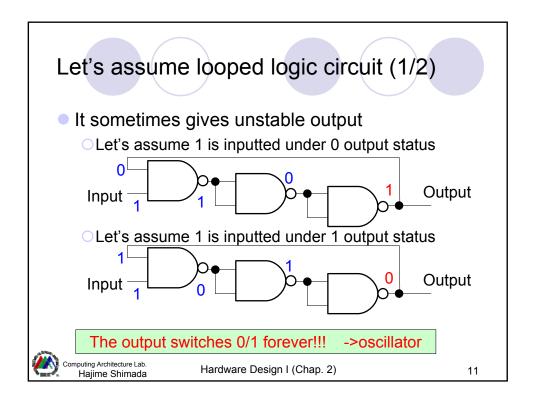

- Combinational logical circuit

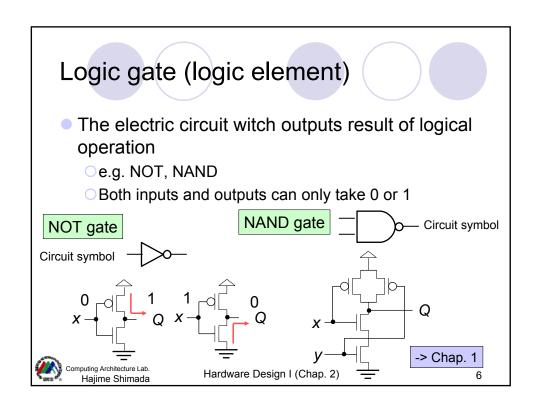

- Logic gate (logic element)Definition of combinational logical circuit

- O How to create output signal?

- Logical function

- Definition of logical function

- O Relationship between logical circuit

- Logical expression

- O Definition of logical expression

- Minterm and maxterm

- Axiomatic systems

- Amount of logical expression

Hardware Design I (Chap. 2)

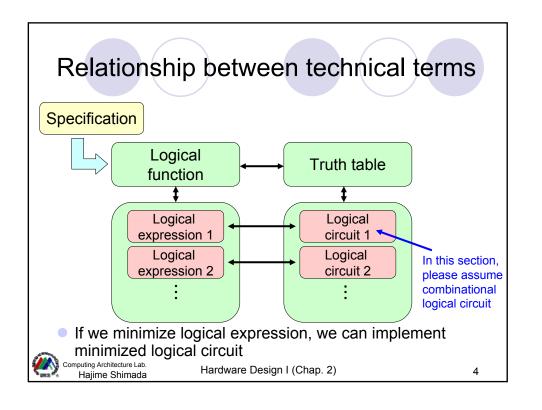

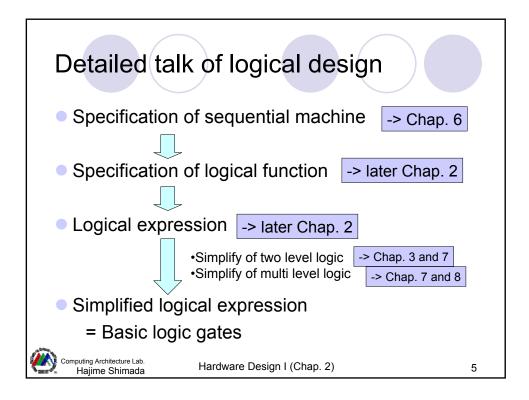

#### Review: outlined flow of LSI design Define specification Definition in hardware description language Architectural design Logic synthesis Circuit with basic logic gates Logical design This chapter treats this area \_ Place and route Mask pattern Logical function Logical expression OPhysical design Manufacturing nputing Architecture Lab. Hajime Shimada Hardware Design I (Chap. 2) 3

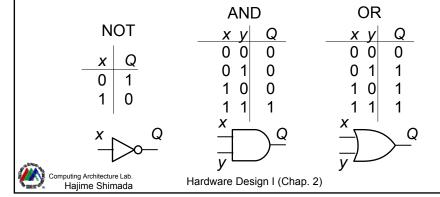

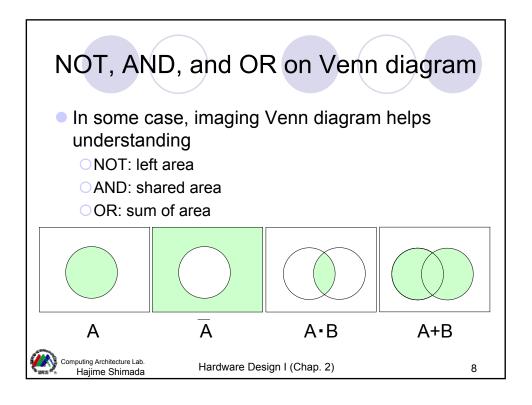

#### NOT, AND, and OR on Boolean algebra

- Logical circuit operates on Boolean algebra

- Here's basic logic from Boolean algebra

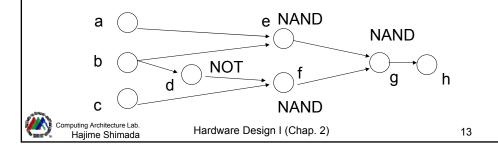

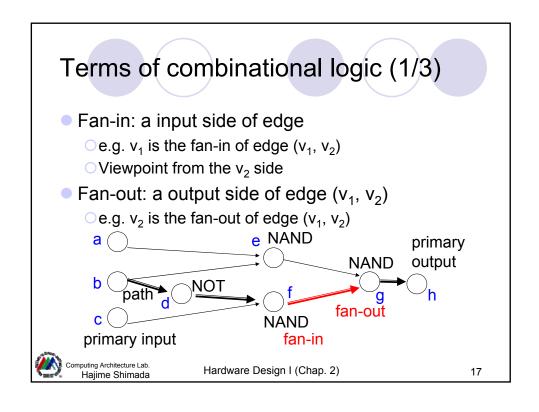

# Definition of combinational logic with directed graph

- Set of vertices: V={a, b, c, d, e, f, g, h}

- Set of edges: E⊆(V × V)

E={(a,e), (b,e), (b,d), (c,f), (d,f), (e,g), (f,g), (g,h)}

- Label of vertex: NOT, NAND, and so on

### If you felt "what is directed graph?" ...

- Please relearn "graph theory"

- The sets of vertices and edges

- oe.g. network connection graph, schematic diagram, ...

- Specific graph: tree, directed graph, weighted graph, ...

- It is widely used in informatics world

- Syntax tree (compiler)

- Markov chain (voice recognition)

- OPerceptron (neural network)

Hardware Design I (Chap. 2)

#### About technical terms of set theory

- Set

- Gathered set of elements

- ○e.g. {0, 1}, {a, b, ..., z}, ...

- Cartesian product

- OA set of ordered pairs of elements

- $\bigcirc$  Notation: A  $\times$  B (A,B: set)

- $\bigcirc$  e.g.  $\{0, 1\} \times \{a, b\} = \{(0,a), (0,b), (1,a), (1,b)\}$

- Other notation: V<sup>2</sup>, {0, 1}<sup>2</sup>

Hardware Design I (Chap. 2)

1

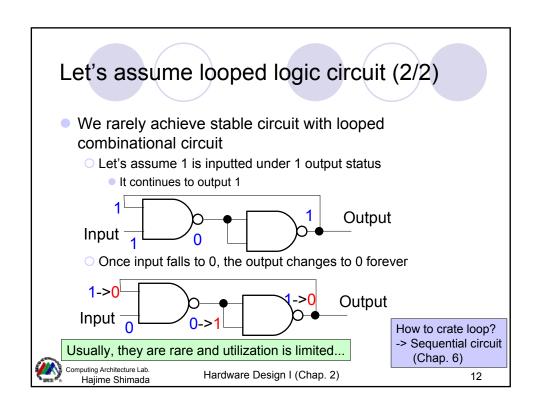

# The syntax of combinational logic from graph theory

- Directed Acyclic Graph (DAG): (V, E)

- V: set of vertices

- $\bigcirc$  E: set of edges, subset of (V  $\times$  V)

- (V × V) denotes set of Cartesian product

- Allocate logic gate (e.g. NAND) label to vertices

- Allocate 1 label to 1 vertex

Hardware Design I (Chap. 2)

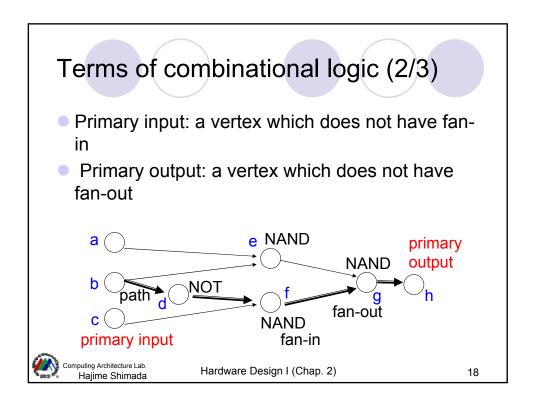

#### Terms of combinational logic (3/3) Path: a set of edges from primary input to primary output $\circ$ e.g. $(v_1, v_2) (v_2, v_3) ... (v_{n-1}, v_n)$ ○v₁ is transitive fan-in ○v<sub>n</sub> is transitive fan-out e NAND primary output **NAND** fan-out **NAND** fan-in primary input puting Architecture Lab. Hajime Shimada Hardware Design I (Chap. 2) 19

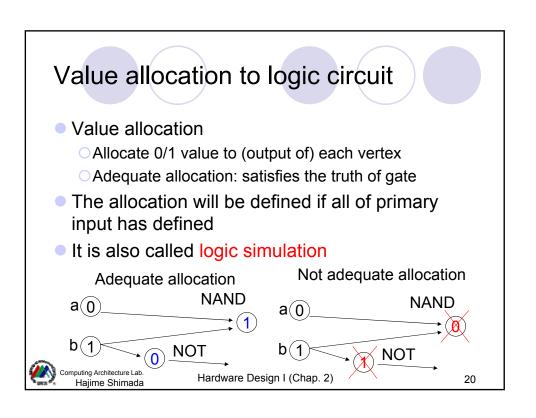

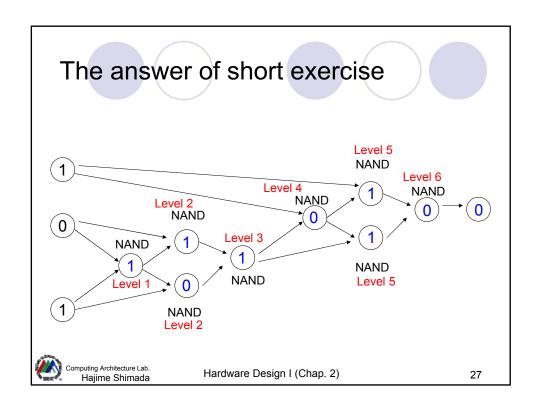

### The algorithm of value allocation

- Define the value of primary inputs

- Primary inputs are called level 0 vertices

- Define the value of level 1 vertices

- Level 1 vertices: all inputs of them are primary input

- All inputs value are already defined in 1.

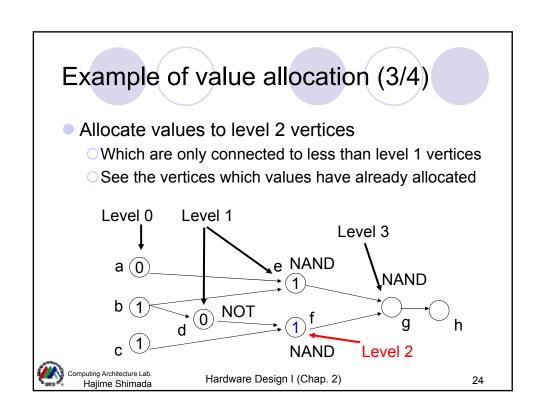

- 3. Define the value of level 2 vertices

- Level 2 vertices: all inputs of them are less than level 1 (level 0 or 1)

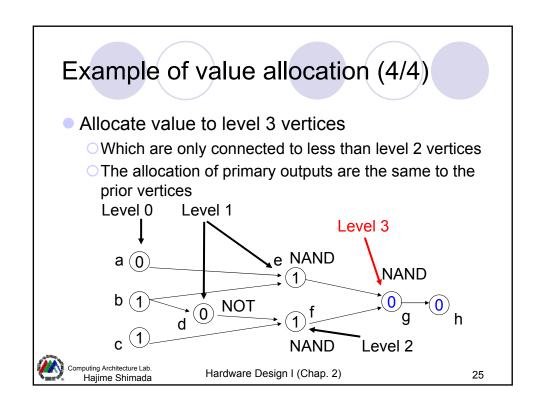

- Define level n vertices until the all of the vertices have defined

- Level n vertices: all inputs of them are less than level n-1

Hardware Design I (Chap. 2)

21

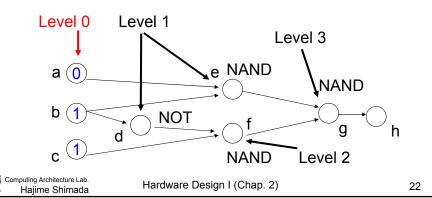

## Example of value allocation (1/4)

- Allocate value to primary inputs (level 0 vertices)

- We can allocate them without constraint

- Ousually, they are given

#### Example of value allocation (2/4) Allocate values to level 1 vertices OWhich are only connected to primary inputs Level 0 Level 1 Level 3 e NAND a (0 NAND NOT **(0)** Level 2 NAND puting Architecture Lab. Hajime Shimada Hardware Design I (Chap. 2) 23

# Definition of logical function from mathematical viewpoint

- Representation of the relationship between input value and output value

- The definition of *n*-value logical function:

#### Projection from $\{0, 1\}^n$ to $\{0, 1\}$

- Subset  $f \subseteq \{0, 1\}^n \times \{0, 1\}$  which does not include both  $(X, 0) \in f$  and  $(X, 1) \in f$  in arbitrary X

- We denote it y = f(X) if  $(X, y) \in f$

- ○{0, 1}<sup>n</sup> is called domain

- ○{0, 1} is called codomain

Hardware Design I (Chap. 2)

29

# Example of definition of 3-value logical function (notated by logical circuit)

- It outputs 0 if we input (0, 0, 0) into it \(^\)

- It outputs 1 if we input (0, 0, 1) into it:

It outputs 1 if we input (1, 1, 1) into it

This is logical function!

# Examples of definition of representative logical function

- The function of NOT  $\subseteq \{0,1\} \times \{0,1\}$

- $\bigcirc$ {(0, 1), (1, 0)}

- The function of AND  $\subseteq \{0,1\}^2 \times \{0,1\}$

- $\bigcirc$ {((0, 0), 0), ((0, 1), 0), ((1, 0), 0), ((1, 1), 1)}

- The function of AND  $\subseteq \{0,1\}^2 \times \{0,1\}$

- $\{((0,0),0),((0,1),1),((1,0),1),((1,1),1)\}$

Input Output

Hardware Design I (Chap. 2)

31

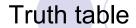

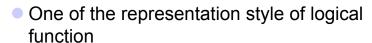

#### Hot to denote them in usual?

- Usually, we do not use mathematical definition

- We usually use following notations

- Logical circuit

- Truth table

- Logical expression

Hardware Design I (Chap. 2)

- Aligning output values for all possible inputs

- The size of n values logical function is 2<sup>n</sup>

| <b>X</b> <sub>1</sub> | <i>X</i> <sub>2</sub> | $f(x_1,x_2)$ | $g(x_1,x_2)$ | $h(x_1,x_2)$    | _                        |

|-----------------------|-----------------------|--------------|--------------|-----------------|--------------------------|

| 0                     | 0                     | 0            | 0            | h(0, 0)         | If truth tables of two   |

| 0                     | 1                     | 0            | 1            | <i>h</i> (0, 1) | functions are identical, |

| 1                     | 0                     | 0            | 1            | h(1, 0)         | the functions are        |

| 1                     | 1                     | 1            | 0            | h(1, 1)         | identical                |

Truth table

Hardware Design I (Chap. 2)

33

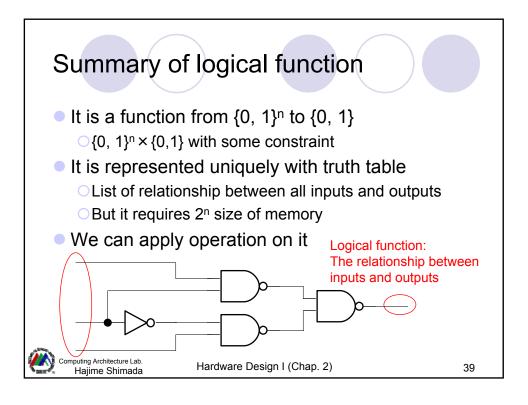

Logical function represents the relationship of input value and output value in combinational logical circuit

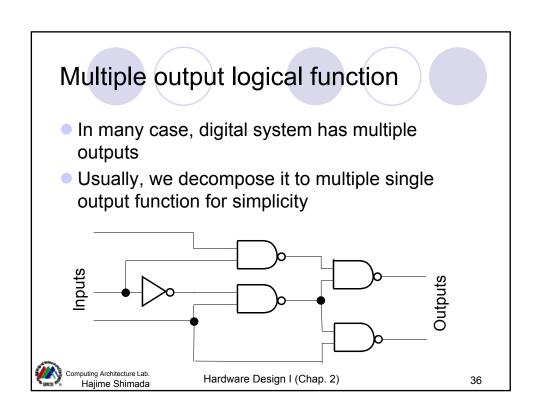

# Truth table of multiple output logical function

Projection from  $\{0, 1\}^n$  to  $\{0, 1\}^m$

OList of m projections from  $\{0, 1\}^n$  to  $\{0, 1\}$

| <i>X</i> <sub>1</sub> <i>X</i> | $f_0(z)$ | $(x_1, x_2)$ | $f_1(x_1,x_2)$ |

|--------------------------------|----------|--------------|----------------|

| 0 (                            | )        | 0            | 0              |

| 0 1                            | 1        | 0            | 1              |

| 1 (                            | )        | 0            | 1              |

| 1 1                            | 1        | 1            | 0              |

Hardware Design I (Chap. 2)

37

### Operation between logical functions

- We can extend operation on logical value to logical function

- $\bigcirc$   $(f \cdot g) (x_1, x_2, ..., x_n) = f(x_1, ..., x_n) \cdot g(x_1, ..., x_n)$

- $\bigcirc (f+g)(x_1, x_2, ..., x_n) = f(x_1, ..., x_n) + g(x_1, ..., x_n)$

- $\bigcirc (f') (x_1, x_2, ..., x_n) = f(x_1, x_2, ..., x_n)'$

- Detail is taught in following logical expression section

Hardware Design I (Chap. 2)

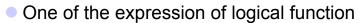

#### Logical expression

- Represent it with arrangement of variable which denotes logical function

- e.g. x + y•z + x•y'•z'

- Efficient than truth table

- But there's no uniqueness

- x = a+b; y = c+d; z = x+y -> z = (a+b) + (c+d)

Hardware Design I (Chap. 2)

41

#### The definition of logical expression

- 1. Logical variables are logical expression

- e.g. x, y, z, x<sub>1</sub>, x<sub>2</sub>, a, b, ...

- If E<sub>1</sub> and E<sub>2</sub> are logical expression,

(E<sub>1</sub>•E<sub>2</sub>), (E<sub>1</sub>+E<sub>2</sub>), (E<sub>1</sub>') are logical expression

e.g. (x•y), (x+y), (x+(y•z)), (x+(y'))

- Generated in recursively

- We can omit brackets by adding order to operations

- Order: ', •, and +

Hardware Design I (Chap. 2)

# The expression of logical function with logical expression (1/2)

- Pay attention to the logical function which has only one "1" output in truth table

- Called minterm

- Minterm can be represented by AND and NOT

| Minterm   |       |       |                                       |     |  |  |  |  |  |  |  |

|-----------|-------|-------|---------------------------------------|-----|--|--|--|--|--|--|--|

| V V       | ابر ا | χ'•γ  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | v-v |  |  |  |  |  |  |  |

| ху        | x'·y' | x · y | x·y'                                  | x·y |  |  |  |  |  |  |  |

| 0 0       | 1     | 0     | 0                                     | 0   |  |  |  |  |  |  |  |

| 0 1       | 0     | 1     | 0                                     | 0   |  |  |  |  |  |  |  |

| 10        | 0     | 0     | 1                                     | 0   |  |  |  |  |  |  |  |

| 1 1       | 0     | 0     | 0                                     | 1   |  |  |  |  |  |  |  |

| ation Lab |       |       |                                       |     |  |  |  |  |  |  |  |

Computing Architecture Lab.

Hajime Shimada

Hardware Design I (Chap. 2)

43

# The expression of logical function with logical expression (2/2)

- The logical function which has multiple "1" output is represented by OR of minterms

- The arbitrary function can be represented with AND, OR, and NOT of logical variable

|   |     |         | Minte | erm  |     |                                    |

|---|-----|---------|-------|------|-----|------------------------------------|

|   |     | ر. ب. ا | ٠, ,, | ر    |     | <b>f</b> ()                        |

| _ | ху  | x'·y'   | x'·y  | x·y' | x.A | $f(x,y) = x' \cdot y + x \cdot y'$ |

|   | 0 0 | 1       | 0     | 0    | 0   | 0                                  |

|   | 0 1 | 0       | 1     | 0    | 0   | 1                                  |

|   | 1 0 | 0       | 0     | 1    | 0   | 1                                  |

|   | 11  | 0       | 0     | 0    | 1   | 0                                  |

Computing Architecture Lab.

Hajime Shimada

Hardware Design I (Chap. 2)

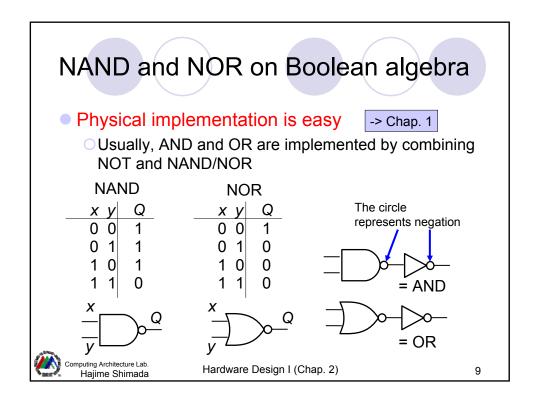

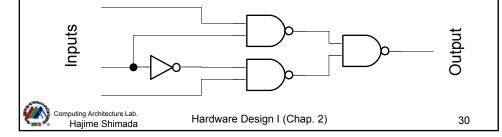

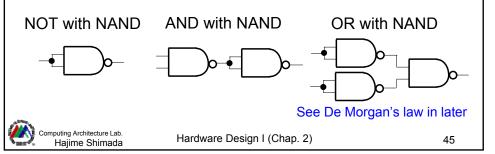

#### Notation only 2-input NAND or NOR

- We can represent NOT, AND, and OR with NAND gates by following wire connection

- OCalled "NAND has functional completeness"

- Similar representation can be done with only NOR gates

### Sum of products

- Definition

- Literal: Logical value or the negation of logical value

- a: positive literal

- a': negative literal

- 1. Create term with AND of literals

- 2. Create logical expression with OR of 1.

- e.g. abc + a'b'c + ac, ac + bc + ad'e

- Other names: AND-OR type, two level logic

- The sum of minterms has special name

- ->Disjunctive Normal Form (DNF)

Hardware Design I (Chap. 2)

### Disjunctive Normal Form (DNF)

OArbitrary logical function can be expressed with DNF

|     | 1      | 1    |   |   |     |    | - 1 |        |     |      |       |

|-----|--------|------|---|---|-----|----|-----|--------|-----|------|-------|

| a b |        | f    | g |   | a   | b  | С   |        | h   | S    | t_    |

| 0 0 | a'b'   | 0    | 1 |   | 0   | 0  | 0   | a'b'c' | 0   | 0    | 1     |

| 0 1 | a'b    | 1    | 0 |   | 0   | 0  | 1   | a'b'c  | 1   | 1    | 1     |

| 1 0 | ab'    | 1    | 0 |   | 0   | 1  | 0   | a'bc'  | 0   | 0    | 0     |

| 1 1 | ab     | 0    | 1 |   | 0   | 1  | 1   | a'bc   | 1   | 1    | 0     |

|     |        |      |   |   | 1   | 0  | 0   | ab'c'  | 0   | 0    | 0     |

| f = | a'b +  | ab   | , |   | 1   | 0  | 1   | ab'c   | 1   | 1    | 0     |

|     | a'b' - |      |   |   | 1   | 1  | 0   | abc'   | 1   | 0    | 1     |

| 9   | uБ     | · ac | , |   | 1   | 1  | 1   | abc    | 0   | 1    | 1     |

|     |        |      |   | h | = a | 'n | c'  | + a'bc | + ; | ab'd | : + a |

h = a'b'c' + a'bc' + ab'c + abc' s = a'b'c + a'bc + ab'c + abc t = a'b'c' + a'b'c + abc' + abcHardware Design I (Chap. 2)

Lab. ada

Computing Architecture Lab. Hajime Shimada

47

#### Product of sums

- 1. Create term with OR of literals

- 2. Create logical expression with AND of 1.

- e.g. (a+b'+c) (a'+b+c)(d+e')

- There's a counterpart notation of DNF

- ->Conjunctive Normal Form (CNF)

- Sum of maxterms

- Maxterm: the logical function which has only one "0" output in truth table

Hardware Design I (Chap. 2)

- Called maxterm

- OMaxterm can be represented by OR and NOT

#### Maxterm

|     | •   |      |      | ,     |                       |

|-----|-----|------|------|-------|-----------------------|

| ху  | х+у | x+y' | x'+y | x'+y' | f(x,y) = (x+y)(x'+y') |

| 0 0 | 0   | 1    | 1    | 1     | 0                     |

| 0 1 | 1   | 0    | 1    | 1     | 1                     |

| 10  | 1   | 1    | 0    | 1     | 1                     |

| 11  | 1   | 1    | 1    | 0     | 0                     |

|     |     | 1    |      |       |                       |

Computing Architecture Lab.

Hajime Shimada

Hardware Design I (Chap. 2)

**4**0

## Conjunctive Normal Form (CNF)

- Sum of maxterms without same maxterm

- OArbitrary logical function can be expressed with CNF

| a b        |        | f    | g        | a | b | С   |        | h | s | _t_ |

|------------|--------|------|----------|---|---|-----|--------|---|---|-----|

| 0 0        | a'b'   | 0    | 1        | 0 | 0 | 0   | a'b'c' | 0 | 0 | 1   |

| 0 1        | a'b    | 1    | 0        | 0 | 0 | 1   | a'b'c  | 1 | 1 | 1   |

| 1 0        | ab'    | 1    | 0        | 0 | 1 | 0   | a'bc'  | 0 | 0 | 0   |

| 1 1        | ab     | 0    | 1        | 0 | 1 | 1   | a'bc   | 1 | 1 | 0   |

|            | 1      |      |          | 1 | 0 | 0   | ab'c'  | 0 | 0 | 0   |

| $f = \ell$ | a'+b') | ′a+k | <b>)</b> | 1 | 0 | 1   | ab'c   | 1 | 1 | 0   |

| •          |        | •    | •        | 1 | 1 | 0   | abc'   | 1 | 0 | 1   |

| g – (      | a'+b)( | a+D  | )        | 1 | 1 | 1   | abc    | 0 | 1 | 1   |

|            |        |      |          |   |   | - 1 |        |   |   |     |

h = (a+b+c)(a+b'+c)(a'+b+c)(a'+b'+c')

s = (a+b+c)(a+b'+c)(a'+b+c)(a'+b'+c)

t = (a+b'+c)(a+b'+c')(a'+b+c)(a'+b+c')

Computing Architecture Lab.

Hajime Shimada

Hardware Design I (Chap. 2)

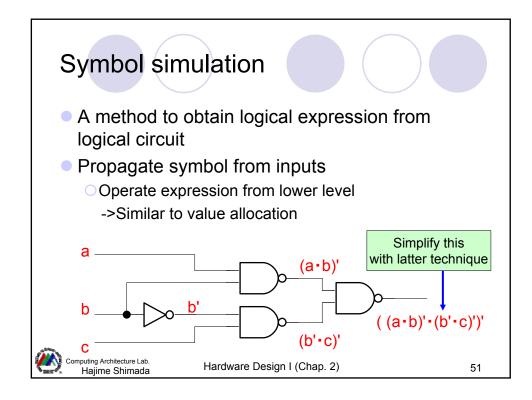

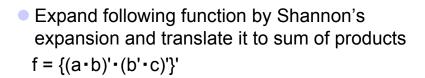

# Simplify with operation on Boolean algebra

- The logical expression given from symbol simulation has complexity

- e.g. ( (a•b)'•(b'•c)')'

- How to simplify them?

- Simplify with operation on Boolean algebra

- General operation rule

- ODe Morgan's law

- Shannon's expansion

Hardware Design I (Chap. 2)

# Axiomatic systems related simplification on Boolean algebra

- General operation rules

- Oldempotent: a+a = a

- Commutativity: a+b = b+a

- Associatively: (a+b)+c = a+(b+c)

- ○Absorption: a+(a•b) = a

- Object Distributive: (a+b)·c = a·c+b·c

- Involution: (a')' = a

- Complements: a+a' = 1

- Oldentity: a · 1 = a

- ODomination: a 0 = 0

Venn diagram

# Axiomatic systems related simplification on Boolean algebra

- Duality

- ○The rule that exchanged "+ and " and "0 and 1" will be approved (Dual rule)

- oe.g. a+a = a ← a•a = a

- $\bigcirc$  e.g.  $a+a'=1 \longleftrightarrow a\cdot a'=0$

- We can insert arbitrary logical expressions into a, b, and c in prior equations

Hardware Design I (Chap. 2)

### Review: 2-input logical operation

- AND, OR, NAND, and NOR: described before

- XOR: output 1 if the inputs are not equal

- XNOR: output 1 if the inputs are equal

|   |   | AND | OR  | NAND   | NOR    | XOR | XNOR     |

|---|---|-----|-----|--------|--------|-----|----------|

| Χ | y | х·у | х+у | (x·y)' | (x+y)' | x⊕y | (x ⊕ y)' |

| 0 | 0 | 0   | 0   | 1      | 1      | 0   | 1        |

| 0 | 1 | 0   | 1   | 1      | 0      | 1   | 0        |

| 1 | 0 | 0   | 1   | 1      | 0      | 1   | 0        |

| 1 | 1 | 1   | 1   | 0      | 0      | 0   | 1        |

|   |   |     |     |        |        | l   | l        |

Hardware Design I (Chap. 2)

5

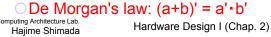

## De Morgan's law

- $(x \cdot y)' = x' + y'$

- $(x+y)' = x' \cdot y'$

- We can insert arbitrary logical expressions into x and y

|   |   | Equ    | Jai   | Equal  |       |  |  |  |  |

|---|---|--------|-------|--------|-------|--|--|--|--|

|   |   |        |       |        |       |  |  |  |  |

| Χ | у | (x·y)' | x'+y' | (x+y)' | x'·y' |  |  |  |  |

|   |   |        |       |        |       |  |  |  |  |

| 0 | 0 | 1      | 1     | 1      | 1     |  |  |  |  |

| 0 | 1 | 1      | 1     | 0      | 0     |  |  |  |  |

| 1 | 0 | 1      | 1     | 0      | 0     |  |  |  |  |

| 1 | 1 | 0      | 0     | 0      | 0     |  |  |  |  |

|   | • |        | J     |        |       |  |  |  |  |

Computing Architecture Lab. Hajime Shimada

Hardware Design I (Chap. 2)

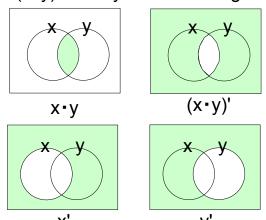

### De Morgan's law on Venn diagram

Here's (x•y)' = x'+y' on Venn diagram

Computing Architecture Lab. Hajime Shimada

Hardware Design I (Chap. 2)

57

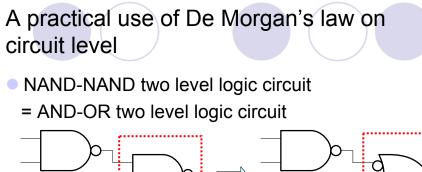

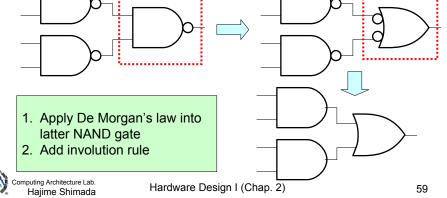

## De Morgan's law on circuit level

- NAND and NOR becomes AND and OR with negated inputs

Computing Architecture Lab. Hajime Shimada

Hardware Design I (Chap. 2)

### Generalized De Morgan's law

$$F'(x_1, x_2, \dots, x_n) = G(x_1, x_2, \dots, x_n)$$

Under

$$Xi \leftrightarrow Xi'$$

$+ \leftrightarrow \cdot$

Widely used when you want to negate arbitrary logical function f

e.g.

$$(a'b'+a'b+ab')' = (a+b)(a+b')(a'+b)$$

= aaa'+aab+ab'a'+ab'b+baa'+bab+bb'a'+bb'b

= ab + ab = ab

e.g.  $((a \cdot b)' \cdot (b' \cdot c)')' = (a \cdot b) + (b' \cdot c) = a \cdot b + b' \cdot c$

Hardware Design I (Chap. 2)

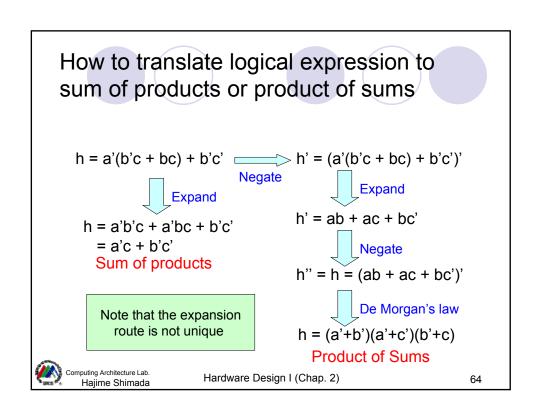

### How to create CNF?

- Sum of "0" term in truth table

- Negate function obtained in 1.

|     | а                      | b | С |                  | h | s  | t     |                                       |

|-----|------------------------|---|---|------------------|---|----|-------|---------------------------------------|

|     |                        | 0 | 0 | a'b'c'           | 0 | 0  | 1     | h' = a'b'c' + a'bc' + ab'c' + abc     |

|     | 0                      | 0 | 1 | a'b'c            | 1 | 1  | 1     |                                       |

|     | 0                      | 1 | 0 | a'bc'            | 0 | 0  | 0     |                                       |

|     | 0                      | 1 | 1 | a'bc             | 1 | 1  | 0     | h'' = (a'b'c' + a'bc' + ab'c' + abc)' |

|     | 1                      | 0 | 0 | ab'c'            | 0 | 0  | 0     | ii = (a b c + a b c + ab c + ab c)    |

|     | 1                      | 0 | 1 | ab'c             | 1 | 1  | 0     | De Morgan's law                       |

|     | 1                      | 1 | 0 | abc'             | 1 | 0  | 1     |                                       |

|     | 1                      | 1 | 1 | abc              | 0 | 1  | 1     | h = (a+b+c)(a+b'+c)                   |

|     |                        |   |   |                  |   |    |       | (a'+b+c)(a'+b'+c')                    |

| Coi | mputing<br><b>Haii</b> |   |   | ure Lab.<br>mada |   | На | ırdwa | are Design I (Chap. 2) 61             |

#### Shannon's expansion

$$f(x_1, x_2, \dots, x_n) = x_1' \cdot f(0, x_2, \dots, x_n) + x_1 \cdot f(1, x_2, \dots, x_n)$$

e.g.

$$(a'b'+a'b+ab')'$$

=  $a'((1 \cdot b'+1 \cdot b+0 \cdot b')')+a((0 \cdot b+0 \cdot b+1 \cdot b')')$

Substitute  $a=0$

=  $a'((\underline{b'+b})')+a((b')')$

=1

=  $a'(0)+a(b'') = ab$

Computing Architecture Lab. Hajime Shimada

Hardware Design I (Chap. 2)

65

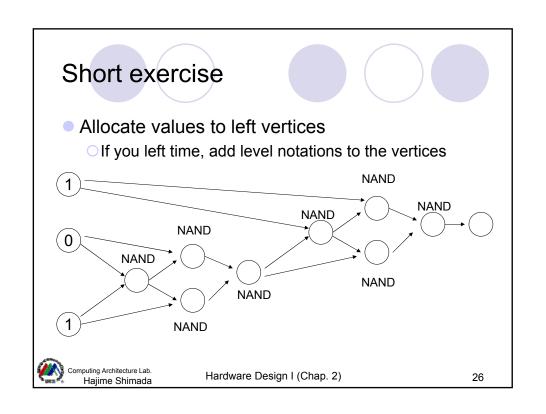

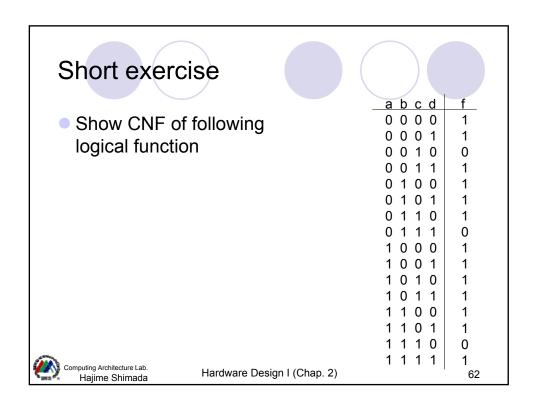

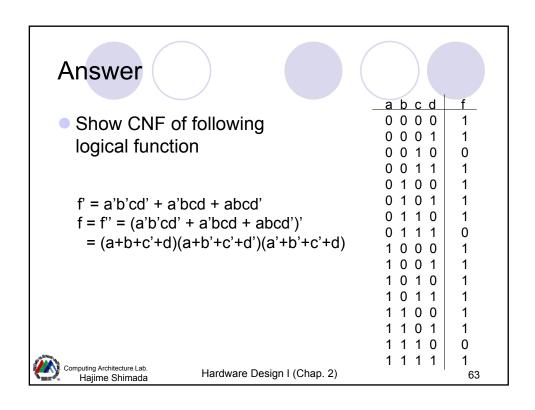

#### Short exercise

Computing Architecture Lab. Hajime Shimada

Hardware Design I (Chap. 2)

#### Answer

$$f = \{(a \cdot b)' \cdot (b' \cdot c)'\}'$$

$$f = a' \cdot \{(\underline{0 \cdot b})' \cdot (b' \cdot c)'\}' + a \cdot \{(\underline{1 \cdot b})' \cdot (b' \cdot c)'\}'$$

$$= a' \cdot \{(b' \cdot c)'\}' + a \cdot \{b' \cdot (b' \cdot c)'\}'$$

$$= b' \cdot [a' \cdot \{(\underline{1 \cdot c})'\}' + a \cdot \{\underline{1 \cdot (1 \cdot c)'}\}'] + b \cdot [a' \cdot \{(\underline{0 \cdot c})'\}' + a \cdot \{\underline{0 \cdot (0 \cdot c)'}\}'$$

$$= c \qquad = c \qquad = 0$$

$$= b' \cdot (a' \cdot c + a \cdot c) + b \cdot a$$

$$= \underline{(a' + a)} \cdot b' \cdot c + a \cdot b = a \cdot b + b' \cdot c$$

Computing Architecture Lab.

Hajime Shimada

Hardware Design I (Chap. 2)

67

## Equivalence of logical function

- There are equivalent logical expression in each logical function

- In logical circuits design, there's possibility that it includes same circuits (= same logical expression)

- -> Redundant! (consume unnecessary silicon resources)

- How to check equivalence of them?

- Ohecking on truth table is one method

- The size of truth table is 2<sup>n</sup> on n-value

- Cogitated algorithm or data structure are required

-> Later Chap. 2

Hardware Design I (Chap. 2)

But there are 2<sup>2<sup>n</sup></sup> of logical functions in n-value logical function

| func                  | 1 | n | _ | )<br>()<br>() | ) ( | )  | Q<br>?<br>?<br>? |      |    | Th   | ere  | e a  | re    | <b>2</b> <sup>4</sup> | pc | ss | ible | out | puts | 3 |

|-----------------------|---|---|---|---------------|-----|----|------------------|------|----|------|------|------|-------|-----------------------|----|----|------|-----|------|---|

| _ x y                 |   |   |   |               |     | '  |                  |      |    |      |      |      |       |                       |    |    |      |     | _    |   |

| 0 0                   | ) | 0 | 0 | 0             | 0   | 0  | 0                | 0    | 0  | 1    | 1    | 1    | 1     | 1                     | 1  | 1  | 1    |     |      |   |

| 0 1                   |   | 0 | 0 | 0             | 0   | 1  | 1                | 1    | 1  | 0    | 0    | 0    | 0     | 1                     | 1  | 1  | 1    |     |      |   |

| 1 0                   | ) | 0 | 0 | 1             | 1   | 0  | 0                | 1    | 1  | 0    | 0    | 1    | 1     | 0                     | 0  | 1  | 1    |     |      |   |

| 1 1                   |   | 0 | 1 | 0             | 1   | 0  | 1                | 0    | 1  | 0    | 1    | 0    | 1     | 0                     | 1  | 0  | 1    |     |      |   |

| Computing Ar<br>Hajim |   |   |   |               |     | Ha | ardw             | /are | De | sign | I (C | Chap | ). 2) | 1                     |    |    |      |     |      | 6 |

Examples of 2-input logical function

- There's possible functions which are not named

- But usually, there's no use

|   |   | AND | XOR |       |       |       |       |

|---|---|-----|-----|-------|-------|-------|-------|

| Χ | y | х•у | x⊕y | (= x) | (= 0) | (= y) | (= 1) |

| 0 | 0 | 0   | 0   | 1     | 0     | 0     | 1     |

| 0 | 1 | 0   | 1   | 0     | 0     | 1     | 1     |

| 1 | 0 | 0   | 1   | 1     | 0     | 0     | 1     |

| 1 | 1 | 1   | 0   | 0     | 0     | 1     | 1     |

|   |   |     |     |       |       |       |       |

Computing Architecture Lab. Hajime Shimada

Hardware Design I (Chap. 2)

#### Quantity of logical function

- $\bigcirc$  28 = 256 in 3-value function

- $\bigcirc$  2<sup>16</sup> = 65536 in 4-value function

- 2<sup>32</sup> = 4294967296 in 5-value function

- $\bigcirc$  2<sup>64</sup> ( $\rightleftharpoons$  1.8 × 10<sup>19</sup>) in 6-value function

- Too hard to check all of them even if we use computer!

- Let's consider how to reduce number of logical functions

Hardware Design I (Chap. 2)

71

### Symmetry logical function

The logical function is symmetry on  $x_i$  and  $x_j$  if outputs do not change under permutation of  $x_i$  and  $x_j$

Example of symmetry:  $f(x_1, x_2) = x_1 + x_2$  (=  $x_2 + x_1$ ) Example of not symmetry:  $f(x_1, x_2) = x_1' + x_2$  ( $\neq x_2' + x_1$ )

- Quantity of logical function becomes 2<sup>n+1</sup> if the function has perfect symmetry

- The outputs do not change under permutation of all variables

- $\circ$ e.g.  $x'_1 \cdot x_2 \cdot x_3 + x_1 \cdot x'_2 \cdot x_3 + x_1 \cdot x_2 \cdot x'_3$

Hardware Design I (Chap. 2)