| 計算機アーキテクチャ関係の研究 |

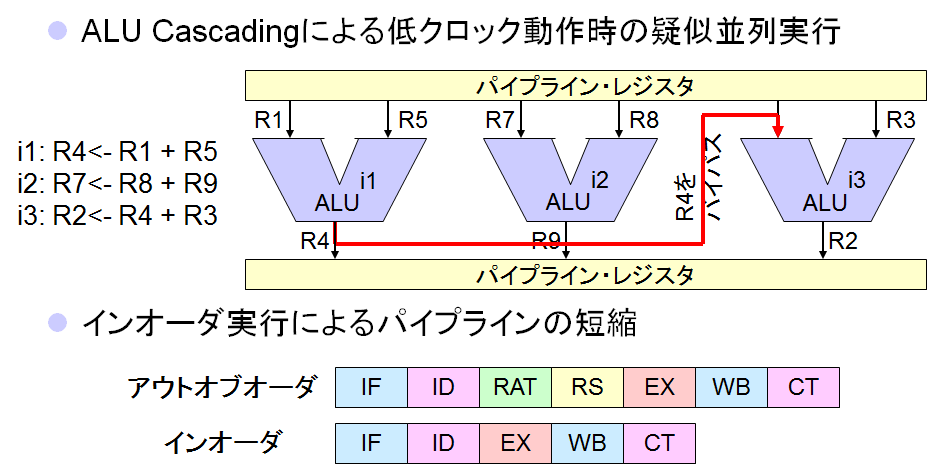

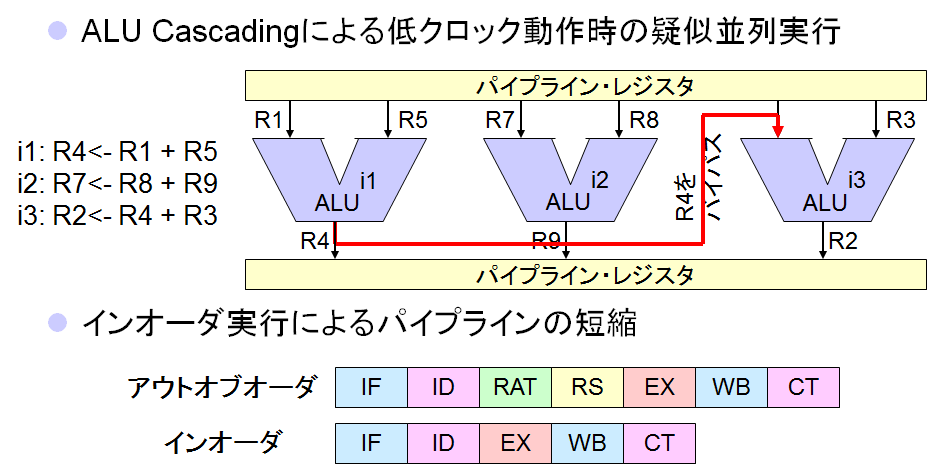

メニーコア・プロセッサに採用されるプロセッサ・コアは面積/エネルギー性能比の良さから高性能組み込 みプロセッサ・コアの流用した2-way インオーダ実行が多い.しかしながら,近年の高性能組み込みコアは性能向上 を目的として2-way アウトオブオーダ実行に拡張される傾向にあるが,アウトオブオーダ実行に付随する回路が必要 となるため,面積/エネルギー性能比が落ちることが考えられる.本論文ではインオーダ実行を拡張する形で,メニー コア・プロセッサに向けた面積/エネルギー性能比の良いプロセッサ・コアについて検討を行った.一般的に,データ 依存によって3-way インオーダ実行の有効性はほぼ無いことが知られているが,近年のプロセッサでは回路として動 作可能なクロック周波数の上限を使うことが少ないことを考え,1 クロック・サイクル中に複数のALU 演算を行う ALU cascading を用いることでこの制限を打破する.提案の有用性を確認するため,SPEC CPU 2000 の整数ベンチ マークを用いて提案するALU cascading を用いた3-way インオーダ実行と2-way アウトオブオーダ実行の性能を比 較した.インオーダ実行によって,アウトオブオーダ実行で必要となるパイプライン・ステージが不要となり,提案 構成のパイプライン段数が2 段削減された場合,提案構成の方が性能が高くなることが確認できた.