Hardware Design I Chap. 2

Basis of logical circuit, logical

expression, and logical function

Computing Architecture Lab.

Hajime Shimada

E-mail: shimada@is.naist.jp

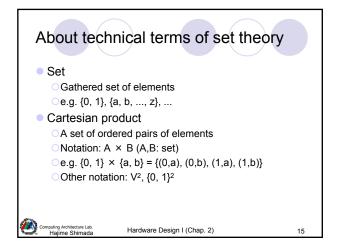

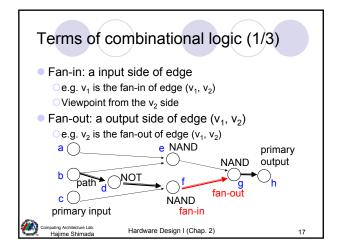

## Definition of combinational logic with directed graph Set of vertices: V={a, b, c, d, e, f, g, h} Set of edges: E⊆(V × V) E={(a,e), (b,e), (b,d), (c,f), (d,f), (e,g), (f,g), (g,h)} Label of vertex: NOT, NAND, and so on a e NAND b NAND b NAND hardware Design I (Chap. 2) 13

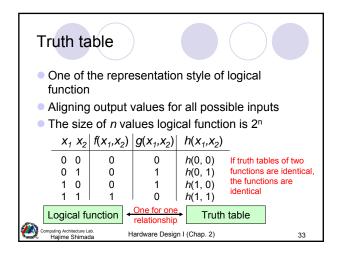

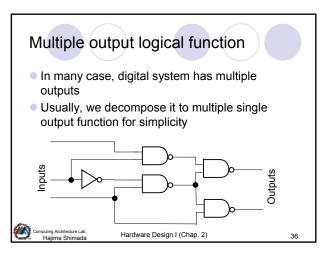

## Truth table of multiple output logical function

Multiple output function (*m* outputs):

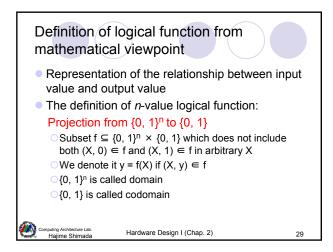

Projection from {0, 1}<sup>n</sup> to {0, 1}<sup>m</sup>

OList of m projections from {0, 1}<sup>n</sup> to {0, 1}

| $X_1 X_2$         | $\int_0^1 f_0(x_1,x_2)$ | $f_1(x_1,x_2)$ |

|-------------------|-------------------------|----------------|

| 0 0<br>0 1<br>1 0 | 0 0 0                   | 0<br>1<br>1    |

Computing Architecture Lab.

Hardware Design I (Chap. 2)

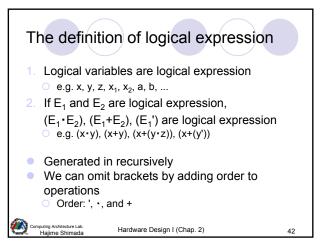

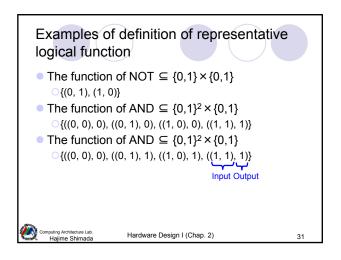

## Operation between logical functions

We can extend operation on logical value to logical function

$$(f \cdot g) (x_1, x_2, ..., x_n) = f(x_1, ..., x_n) \cdot g(x_1, ..., x_n)$$

$$(f + g) (x_1, x_2, ..., x_n) = f(x_1, ..., x_n) + g(x_1, ..., x_n)$$

$$(f') (x_1, x_2, ..., x_n) = f(x_1, x_2, ..., x_n)^t$$

Detail is taught in following logical expression section

Hardware Design I (Chap. 2)

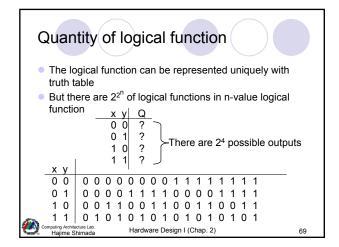

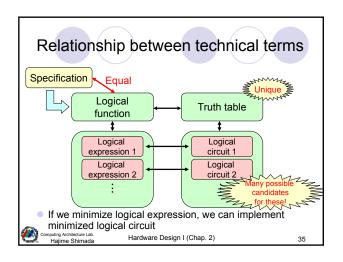

Summary of logical function

It is a function from {0, 1}<sup>n</sup> to {0, 1}

{0, 1}<sup>n</sup> × {0,1} with some constraint

It is represented uniquely with truth table

List of relationship between all inputs and outputs

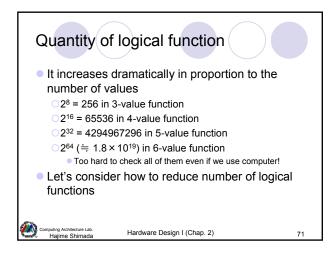

But it requires 2<sup>n</sup> size of memory

We can apply operation on it

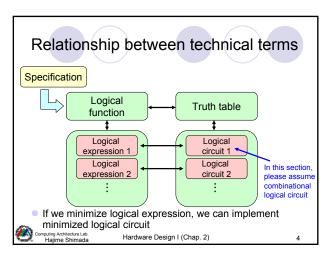

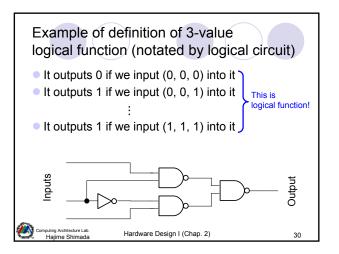

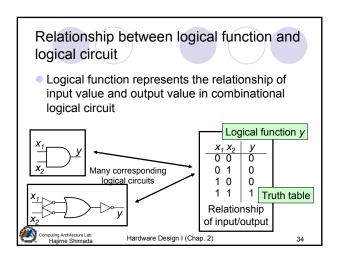

Logical function:

The relationship between inputs and outputs

and outputs

Hardware Design I (Chap. 2)

##